Application Separation

PikeOS offers strict partitioning and strong separation to provide built-in Security by design.

Hardware Consolidation

Extreme flexibility provides independence from suppliers in the choice of hardware architectures.

Use of COTS

The benefit of using Commercial-Off-The-Shelf (COTS) components is to lower overall costs for applications.

PikeOS Compatibility

+80% of the original code base makes the available PikeOS documentation and certification artefacts reusable.

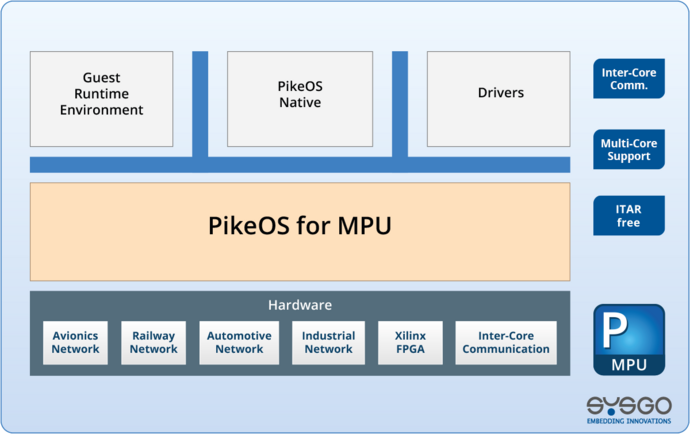

Inter-Core Communication

PikeOS instances on different cores can communicate with each other via message-based communication channels.

ITAR free

As an European company, our products have no export restrictions and are therefore ITAR free.

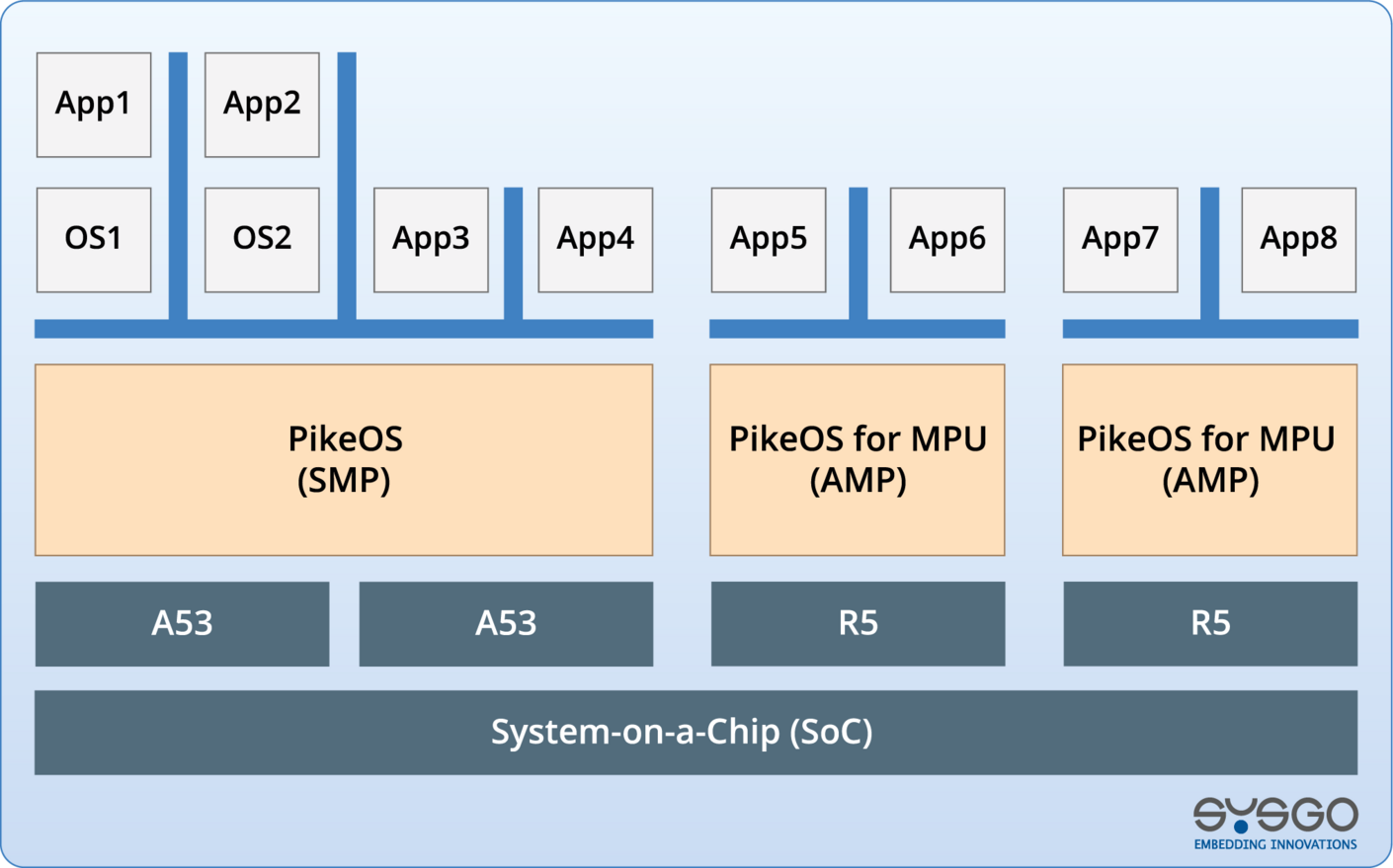

Certifiable MPU and MMU Cores

When using heterogeneous SoC (Systems-on-a-Chip) customers can profit from one PikeOS IDE for the configuration of certifiable MPU and MMU cores

Avionics Customers

Avionics customers can benefit from the ARINC 653, Part 1 compliant configuration

Space Applications

PikeOS for MPU supports less complex hardware which mitigates SEU effects. Great for SPACE applications

Automotive Market

Support for systems with heterogeneous processor core such as the Xilinx Ultrascale+ which is widely used within the Automotive market

Safety & Security Bulletins / Patches

PikeOS for MPU offers Safety & Security bulletins / patches. Step by step, we enlarge Security add-on technologies, such as TSL, SSL or encryption libraries to help making systems more secure

PikeOS Native API

Enhanced PikeOS native API allows migration from software running on proprietary operating systems as well as usage of open-source projects

ITAR free

Less export compliance issues with PikeOS and PikeOS for MPU